Three EECS Teams are winners in 2011 DAC/ISSCC Student Design Contest

The contest is highly competitive and features the best student projects from the largest and most prestigious conferences in their respective fields.

Three University of Michigan student teams were named winners in the 2011 Design Automation Conference (DAC)/International Solid-State Circuits Conference (ISSCC) Student Design Contest, an international contest whose aim is to promote excellence in the design of electronic systems. The winnings designs were featured at a poster session at the ISSCC in February, and will receive their awards at a ceremony at DAC in June.

The contest is highly competitive and features the best student projects from the largest and most prestigious conferences in their respective fields. This is the first time three winners have come from the same institution. They share the honor with 5 other teams from the U.S. and abroad. The winning entries from Michigan:

Enlarge

Enlarge

Enlarge

Enlarge

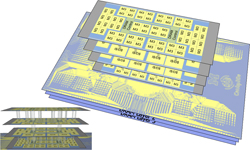

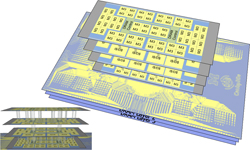

Design and Implementation of Centip3De, a 7-layer Many-Core System, by graduate students David Fick, Ronald G. Dreslinski, Bharan Giridhar, Gyouho Kim, Sangwon Seo, Matthew Fojtik, Sudhir Satpathy, Yoonmyung Lee, Daeyeon Kim, Nurrachman Liu, Michael Wiekowski, Gregory Chen, and Prof. Trevor Mudge, Prof. Dennis Sylvester, and Prof. David Blaauw.

Centip3De stacks circuits in 3D to simultaneously save energy and increase performance in ultra high performance, energy efficient, general purpose computing. It leverages unique aspects of near-threshold computing (NTC), pioneered at Michigan, in conjunction with the emerging technology of 3D integration using through-silicon vias to create highly energy efficient computation clusters, achieving energy efficiency improvements of >5x compared to state-of-the-art commercial multicore processors today.

Centip3De is a a near-threshold 7-layer 3D system that contains 128 ARM Cortex-M3 cores and 256MB of stacked DRAM. It is believed to be the most ambitious circuit design ever undertaken at a university, totaling 93 million transistors across four 3D-stacked silicon layers.

Enlarge

Enlarge

Enlarge

Enlarge

A Flexible Wireless Receiver System with a 7b 21 MS/s Filtering SAR ADC, by graduate students David T. Lin, Li Li, John Bell, Ming-Hao Wang and Prof. Michael P. Flynn.

In order to deal with a rapidly changing wireless communication landscape, the researchers break from traditional design methodology to create a more flexible system that receives and displays images in real-time across multiple standards and bands. The wireless receiver system includes a flexible wireless receiver IC, a custom support and interface daughter-board, and a digital post-processor implemented on an FPGA.

This complete wireless receiver system combines a custom multi-band, multi-standard 65nm CMOS receiver IC with a real-time baseband demodulator on an FPGA to create a full-functioning wireless demonstration system. The key feature of this system is its ability to adapt to its environment and to different communication standards. The performance of this receiver is verified with both the 915MHz and 2450MHz bands of IEEE 802.15.4 and IEEE 802.11.

Enlarge

Enlarge

Enlarge

Enlarge

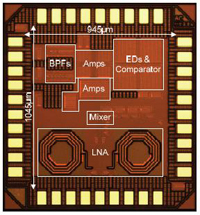

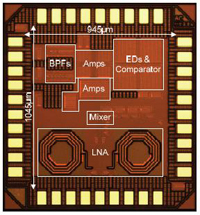

A 1900MHz-Band GSM-Based Clock-Harvesting Receiver with -87dBm Sensitivity, by graduate student Jonathan K. Brown and his advisor, Prof. David D. Wentzloff.

Wireless sensor nodes (WSN) are rapidly reaching a long-sought after reality of shrinking to the size of cubic millimeter computing. As they scale to this size, keeping power consumption to a minimum is critical. In this project, a clock-harvesting receiver (CRX) is designed for low power WSNs, taking the place of existing wake-up receivers (WRX) in order to conserve the maximum energy possible. A WRX uses a wireless signal to wake up sensor nodes periodically to take measurements; it stays on perpetually and determines when to wake up the sensors. However, this CRX extracts a 21-Hz clock embedded within the GSM standard to wake up a sensor node, eliminating the need for a high-power synchronization beacon generated within the energy-constrained WSN.

Measurements show that the receiver achieves -87dBm sensitivity while consuming only 126µW. In sleep-mode, the power consumption is 81pW.

MENU

MENU